随着生成式人工智能(AI)的持续火爆,市场对于高性能AI芯片的需求,也带动了此类AI芯片内部所集成的高带宽内存(HBM)的需求爆发。

根据市场研究机构Gartner的预测,2023年全球HBM营收规模约为20.05亿美元,预计到2025年将翻倍成长至49.76亿美元,增长率高达148.2%。

作为HBM市场的领导厂商,SK海力士最新公布的2023年财报也显示,受益于AI市场的需求,其HBM3的营收较2022年增长了5倍以上。

去年年底,韩国媒体还曾爆料称,已分别向SK海力士和美光预付了7000亿至1万亿韩元的预付款,用于订购大量 HBM3e内存,为其 AI 领域的下一代产品做准备。

不久前美光CEO Mehrotra也曾指出,其专为AI、超级计算机设计的HBM3E预计2024年初量产,有望于2024会计年度创造数亿美元的营收。Mehrotra还对分析师表示,“2024年1~12月,美光HBM预估全数售罄”。

目前HBM市场的供应商只有SK海力士、三星、美光三家,且产能都比较有限。

数据显示,在2022年HBM市场中,SK海力士占据50%的市场份额,三星占比40%,美光占比10%。

而HBM产能供应上的瓶颈,也与CoWos封装产能瓶颈有关,这也同样是英伟达(NVIDIA)等的AI芯片的供应瓶颈。

一、HBM难在哪?

HBM全称为High Bandwidth Memory,即高带宽内存,与常规的DDR DRAM不同,HBM是将很多个DDR DRAM芯片堆叠在一起,然后与GPU/GPU封装在一起,实现大容量、高带宽、低延迟的DDR DRAM组合阵列。

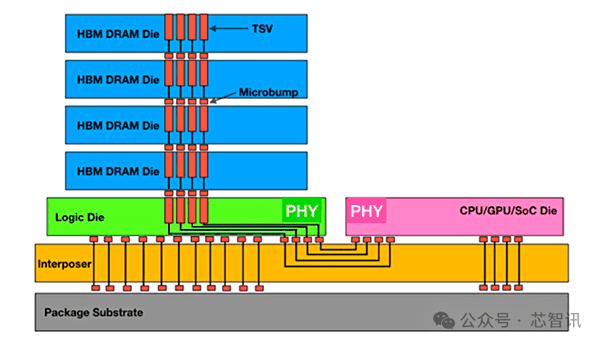

如下图,HBM是将多个DRAM堆叠在一起,Die之间通过TVS硅通孔和Microbump连接。DRAM下面是则是DRAM逻辑控制单元, 对DRAM进行控制。

CPU/GPU和DRAM堆栈通过uBump和Interposer(起互联功能的硅片)连通。Interposer再通过Bump和 Substrate(封装基板)连通到BALL。最后BGA BALL 连接到PCB上。

正如前面所说,HBM可以带来大容量、高带宽、低时延、占用面积小等优点,但是同样也面临着技术难度高、良率、高成本、散热等方面的问题。

比如,HBM依赖昂贵的硅中介层和 TSV工艺来制造,并且HBM 的 2.5D 结构会产生热量,而靠近 CPU 和 GPU 的布局又会加剧这种情况。

另外,HBM走线长度短、焊盘数高,在PCB甚至封装基板上无法实现密集且短的连接,因此还需要CoWoS等2.5D先进封装技术来实现。

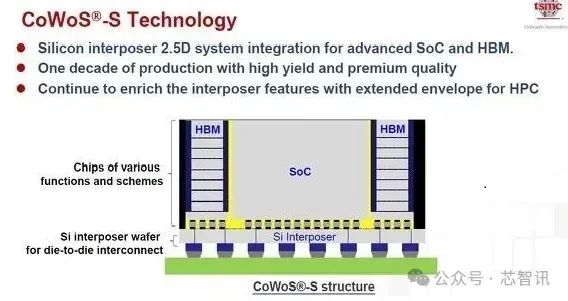

CoWoS能以合理的成本提供更高的互连密度和更大的封装尺寸,目前大部分HBM均使用的此项技术。

因此,无论是对于HBM来说,还是对于高性能的AI GPU来说,他们的产能都将受制于CoWoS产能。那么2024年,HBM的代工产能情况如何?国内是否有国产化HBM及其封装工艺的替代?

近日,知乎答主@Morris.Zhang 发文对此进行了分析:

二、HBM芯片的代工产能测算

@Morris.Zhang 认为,2024年SK海力士、美光、三星这三家的HBM产能会扩产到75万片/年,以12层的HBM3e当前良率90%计算,约可切出750颗/wafer,即2024年全球总计能够产出超过5600万颗的HBM产能(12层 + 8层),上半年产能比例略小;12层HBM颗粒的渠道单价测算是$250+/颗,那么此前传闻的英伟达斥资约13亿美元预定的HBM订单,仅能预定520万颗,仅占2024年总产能的小部分。

补充说明:12层HBM颗粒的渠道单价测算$250+/颗,价格相比一年前略有上浮;换一个测算角度:目前在AI-HPC计算芯片上,通常6颗容量16GB的HBM3颗粒的合计成本约$1500+,相当于$15.6/GB;换算到H100 SXM5,6颗HBM3 80GB,相当于$18.75/GB,约占芯片物料成本的50%+。

倘若基于2024年CoWoS产能来算:

英伟达预定了至少约14+万片wafer(包含台积电12万片以及作为第二供应商的Amkor 2-3万片产能,后者良率较低),设想平均38%良率切出450+万颗GPU,那么每GPU搭配6片颗粒,即需要至少2700+万颗HBM,意味着英伟达仅采购HBM都需要花费68亿美元。

倘若按照2024年全球的GPU+HBM组合的产能来算:

截至Y24-Q4,各家CoWoS GPU产品的预定产能大约900万颗,结合明年三家HBM原厂的扩产计划总计近6000万颗HBM(12层为主,8层略少);这两份供应数据就是吻合的。同时也说明2024年的CoWoS和HBM产能都是充足的。

不过虽然产能不缺,但是上述数据毕竟是“年度计”,很多产能直到Y24-Q4才会开出,而各家预定的产能当然是越早越好,时效性是关键条件,上半年初的机会窗口更重要,倘若下半年才开始投产,黄花菜就凉了。

注释 1:上述谈到的CoWoS全球封装产能是估算约30万片wafer,包括台积电27万片 + 安靠4万片(估算晶圆数据约有1万误差,且后者作为second source的Amkor良率很低);

以及,这些晶圆流片的工艺节点都集中在5nm和3nm,因此yield%保守平均估计在最高38%,约切出900万颗GPU die;每颗GPU搭载6片HBM颗粒是假定最小配置,如AMD MI300 GPU是搭配8片HBM颗粒。则2024年全球的HBM颗粒总需求估算为5500万颗(12层为主)。

诸如英伟达RTX系列使用GDDR6颗粒的消费卡,不会算入CoWoS产能;上述的英伟达14万片wafer是特指Hopper和B100(5nm/3nm),估算2024年英伟达HBM颗粒订单需求是2700万颗。

注释 2:虽说三星也计划导入全栈CoWoS,但了解到2024年可能开不出产能,2025年可能对三星更有利,作为同时供应HBM和CoWoS的IDM,工艺特点和价格优势是显见的。

其次,诸如UMC和GlobalFoundries等产线也可以做前道65nm interposer(但是这两家的工艺节点微缩到14nm就停止了,没有先进制程),因此即不能代工前道的先进工艺logic和interposer,也不能完成一条龙的CoWoS全栈。

另外,倘若Y25 INTC IFS 独立运营,其封装方案也值得观望。

三、HBM及其封装工艺的国产替代

- HBM存储颗粒的国产化

H100芯片的物料成本保守测算在$3300+,其中50%-60%都是HBM3(6颗粒),80GB容量花费的单位成本相当于$18.75/GB;除了Logic Area之外的其它物料(晶圆、封装前后、基板等物料)都是标准定价。

当前我们看到HBM全球库存和渠道周转十分紧张,实际原因是供应商仅有SK Hynix一家,恰逢AI大语言模型趋势带来的HBM需求高峰。

2024-2025年,三星、美光的HBM产能都会陆续开出,各厂提前预订产能,渠道也会随之松弛下来,届时甚至现货市场的HBM颗粒都可以直接采购,演变成DRAM现货渠道的业态。

但是谈到国产化,韩美三家内存厂的HBM是否可以供应给国内?

该问题要从“三个方式”来看:

一则三家内存厂不会直接走ToB集成合同供货给国内客户,特别是某些受限的企业;

二则国内厂商可以直接从现货渠道采购HBM颗粒,进而再适配控制器、适配I/O和逻辑封装;

三则国内厂商可以直接从现货渠道采购DRAM颗粒,进而再通过封装工艺堆叠成HBM,再适配控制器、适配I/O和逻辑封装。

针对“第二、第三种方式”做进一步解读:

第二种方式:单就HBM颗粒而言,目前Hynix HBM的产能紧张是出于供需失衡,而非出于政策限制。

因为,存储颗粒是一种标准品SKU,无需针对颗粒本身做客户化定制,于是这个品类就产生了所谓现货市场。

标准现货是可以通过渠道或分销平台正常流通的,即倘若2024年三家内存厂的产能开出,则全球各区域的代理商库存都会充足,无数的次级渠道/次级代理商都可以无限转售;因此,只要现货库存充足、价格趋势向好,现货市场便永远可以拿货,这是内存颗粒的产业特性。

因此,倘若某些受限的国内厂商需要HBM,而不能获得SK海力士的合同供货和集成定制,则可以从现货市场采购,其它国内厂商也可以效仿,即直接从现货渠道采购HBM颗粒,进而再适配控制器、适配I/O和逻辑封装。

推测昇腾搭载的HBM就是现货渠道采购的HBM或2D-DRAM颗粒,重新堆叠封装后的产物(采购2D-DRAM再堆叠封装的方式属于“第三种方式”)。

第三种方式:相比第三种方式更多一道工序,即堆叠封装,需要攻克几个技术课题。国内有1-2家专业厂商可以从事这种工作:通过从现货市场采购2D-DRAM颗粒,再通过TSV垂直方向通孔、Hybrid Bonding键合的封装工艺实现堆叠出一个HBM器件。

需要指出的是,2023年下半年,佰维存储在东莞松山湖高新区落地了一套封装产线“晶圆级先进封测制造项目”,该厂区项目的另一个实施主体是“芯成汉奇半导体”(佰维持股70%),项目主题是通过TSV和混合键合工艺实现针对DRAM颗粒的多层堆叠封装,甚至是异质集成。

假以时日,该厂应该可以稳定供应国内部分厂商的HBM需求,甚至搭建起国内封装的HBM现货渠道和合同定制服务,推测初代产品可能会在较高的线宽节点堆叠(同时受限于interposer和CoWoS),颗粒密度小一些,频率/位宽/带宽规格小一些,但未来可期。

还有第四种方式:自主研发HBM颗粒和器件。

国内希望拿到三家HBM内存原厂的HBM合同供货和集成定制,但是受到BIS禁令限制;那么除了上述两种方式获得HBM内存,还可以寄希望于自研产品。

国内厂商SwaySure、长鑫都在自主研发HBM,前者进度更快。二者都有来自台湾的研发高管,DRAM颗粒没问题,但目前没有产品化的SKU,HBM则可能要期待2025年或更长时间。

内存/显存作为核心计算设备,它的自研不是由存储厂商独立完成,需要“现代计算Hierarchy的各层厂商”全部参与其中,成熟的通用主存/显存器件需要适配主板PCB和主芯片,还有控制器、协议、底层PHY的搭配设计都很重要,因此HBM基本是与主芯片厂商同步做研发和集成的。

另外,从封装工艺角度,产业化HBM的另一个阻碍在于封装,受限于interposer和CoWoS。

- CoW+WoS封装的国产化

参考GPU芯片构型,倘若缺少CoWoS封装结构,HBM都无处摆放。

目前全球可选的CoWoS产能供应商有几个类别:

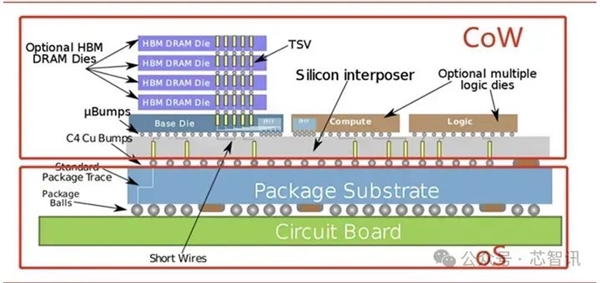

其一是台积电的CoWoS;

其二是由台积电完成晶圆和前道interposer的制造(即CoWoS的“CoW”部分,堆叠+互连),随后交由自家封装厂(例如空闲的InFO产能)或是合作第三方OSAT封装厂完成“on Substrate”部分,即封装在基板上;

其三是可委托由UMC/GF生产interposer,随后再送交Amkor或日月光等OSAT产线,委托完成“WoS”部分;

其四是三星I-Cube/H-Cube和Intel Foveros,两家都可以完成全栈CoWoS交付;

其五是国内也有一部分CoWoS的能力,但几乎全部是CoW+WoS的工艺对接。

诸如UMC和GlobalFoundries等产线可以完成CoW部分的制造,即前道interposer,工艺节点基本在65nm(这两家的工艺节点微缩到14nm就停止了,没有先进制程);因此这类厂商即不能代工前道的先进工艺logic和interposer,也不能完成一条龙的CoWoS全栈。

能够独立完成较高工艺节点、较高良率的全栈CoWoS的厂商,唯有TSMC/Samsung/INTC。

对于国产化的CoWoS封装厂商,盛合晶微和通富微电都有从事Chiplet封装,兼顾包括前道interposer的生产。

通富微电也在国内和海外分别设有厂区;此前传闻称AMD MI300 CoWoS的封装代工会委托给通富微电,但随后证实是误传,实际情况是:AMD曾计划将封装的bumping工序委托给通富微电(槟城工厂),但最终没有合作;通富微电主要是服务于国内。盛合晶微和通富微目前还存在一些良率缺陷,拉动良率是一个缓慢的过程。

其实相比其它制造工序而言,CoWoS并没有极度前沿的技术门槛,唯一的关节是它要保证在高微缩制程下的高良率,因为在封装层面,倘若出品有较高的不良/失效,那么上面堆叠连接的HBM等等器件就变成无可挽回的损耗了;通过兼顾较高工艺节点和良率的,目前唯有台积电。单就CoW+Wos产能而言,全球可以开出很多产能(尤其WoS厂商),但是能够适用于先进计算芯片的工艺/良率的产能则并不多。

出于微缩IC面积,CoWoS的方法就是在Substrate上面增加一层Si interposer,芯片依然通过覆晶方式正面朝下连接在这个中介层上;它就承担die-die互连以及die-substrate互连。

由于interposer是按芯片工艺制造(如初代的65nm),其布线密度可以非常细密(初代<10um),die-die之间也可以堆叠更紧密。

导致上述良率门槛的原因是工艺:以WoS良率为例,难点主要在于其封装的中介层尺寸应当有严格限制,即Si interposer面积需要大于其上面2个甚至多个die的尺寸之和。

然而随着这个尺寸越来越大,CoWoS-5甚至通过一种"2-way lithography stitching approach技术"使得interposer尺寸可以扩到2500nm2(接近3x reticle limit,6代CoWoS尺寸甚至接近4x reticle limit),那么随之带来的工艺风险就是,on wafer边缘的扭曲、接角的垂直凸变问题就会发生,导致封测后不良。而TSMC CoWoS工艺磨合了10几年,积累大量knowhow,才获得如今可靠的高良率。

对于OSAT专业封装厂(包括Amkor/日月光等),导致工艺良率拉升缓慢的因素还有就是与前段interposer的分开制造,虽然CoW+WoS是合理的产业链分工,但是拉升两者共同出品的良率需要两家工艺同步发展。

国内的interposer基本是由SMIC制造,再将其委托给OSAT专业封装厂完成WoS封测;而倘若不能获得SMIC interposer制造,也可以委托UMC/GF代工。

如今,SMIC interposer虽然做不到3nm,但可以使用7nm代替;而且SMIC的先进封装工序也是独立出来,成立子公司运行。

能够独立完成较高工艺节点、较高良率的一条龙全栈CoWoS的厂商,唯有台积电、三星、Intel(Logic die+interposer+CoWoS)。

未来的趋势,可能全球大部分2.5D封装都会是前道-后道合作的模式;前道Fab提供interposer做CoW,后道有载板的做WoS。另外,CoWoS也会更多下沉适用到其它场景,非移动装置涉及AI-HPC的未来大部分产品都会依赖CoWoS封装,2.5D/3D封装目前来看还是Foundry相比OSAT更具优势。